- Technologies

- Privacy Policy

Latest Research topics in vlsi design

Latest research topics in vlsi design.

If we narrow down our discussion to research in areas like electronics, electrical, computer science, artificial intelligence , wireless communication and related fields, which are the base of everything in this high-tech world. In these fields researchers have developed applications (aided with technology) for every field ranging from biomedical to aerospace and construction, which were nowhere related to electronics or even current.

As the research fields we are talking about are providing base to the developing world and providing it with reliable technologies which are being used in real time, the work of researcher becomes more wide starting with an idea to the realization of the idea in the real world in form of application or product.

To make a reliable and working model the idea of the VLSI design project ( i.e speech processing application, biomedical monitoring system etc) needs to be implemented and re-implemented, re-tested and improvised. The there are many development cycles and techniques available which eases up the implementation like:

- Behavioral simulation

- Software based model

- Hardware Implementation (ASIC)

- Programmable hardware (FPGA)

- Co-simulation

Behavioral simulation is used at initial phase and it is not appropriate for testing the real time behavior of the system in actual environment as it is more close to systems behavior in ideal environment.

We can simulate the actual environment by using different software models (more like software models of channels used to test communication systems) but its capabilities are also limited to human capability to model the environmental conditions in mathematical equations and models.

All of us are familiar with ASIC, their high performance and hardwired implementation. These are good for final implementation but not for intermediate stages of implementation and testing. Nothing is better than ASIC for real time testing of analog VLSI circuits. But for digital circuits and DSP applications we have a better option of FPGA (Field Programmable Gate Array).

The hardware co-simulation is a good idea to test and monitor systems in real time. To get more details about PhD thesis in VLSI you can do online research or contact us.

latest Low power research topics in vlsi design

The Research Support Centre provides expert advice and support across the whole Engineering and Technical research lifecycle, from discovery through exploitation of technical and translational research. The centre has two primary functions:

- i) to facilitate the delivery of the Engineering Sciences research strategy and to build partnerships andii) to bring together all the technical research management and support services for Students.

To achieve these goals the centre is made up of two inter-relating components. The Academic Research Support Centre consists of the Research Coordination Office, Platform Technologies team and a Translational Research Office. The Technical Research Support Centre is made up of the Joint Research Office.

The Research Support Centre encompasses a wide range of expertise and facilities. By coordinating these resources, we can provide researchers with a package of support that is integrated, high quality and streamlined – and clearly accountable.

Once a researcher has a proposal for high quality research that will benefit, they can access all the help and resources they need through one gateway. This includes support with the approval process and funding applications and help setting up technical trials.

VLSI PHD Projects

Our research interests cover low power processor architectures, low power circuit design techniques, analog and mixed signal circuit design, rapid prototyping of digital systems, reconfigurable processors, Digital arithmetic, advanced processor architectures, vlsi implementation of signal and image processing algorithms, testing verification, memory design, Embedded vlsi and asynchronous circuits.

Organization engaged with embedded commodity development and serving various business solutions such as

- Embedded System Product Development,

- Software services,

- Android development,

- Web development.

Description for “Ph.d guidance with project assitance” Ph.d/ M.Phil PROJECT ASSISTANCE We look forward to welcoming you to one of our “Research and Development Division” for all Ph.D., Research scholars. We will arrange you the following details for completing your Ph.d Degree

- Any University Admission- We provides a step-to-step guide to completing the application form, and will help make the process as straight forward as possible.

- Guide Arrangement

- Survey Paper Preparation

- Problem Identification –Problem Identification of Existing System.

- Implementation in all domains

- Mobile Ad hoc Networks

- Wireless Networks

- Image Processing

- Grid Computing

- Distributed Computing

- Natural Language Processing

- Cloud Computing

- Soft Computing

- Data Mining

- Wireless Senor Networks

Delivering effective support on your Ph. D work:

Companies represents a simple and practical advice on the problems of getting started, getting organized with the working on Ph.D projects.

We make you understand the practicalities of surviving the ordeal. We just make you divide the huge task into less challenging pieces. The training includes a suggested structure and a guide to what should go in each section.

We afford complete support with real-time exposure in your Ph.D works in the field of VLSI. Our Mission drives us in the way of delivering applications as well as products with complete integrity, innovative & interesting ideas with 100% accuracy.

- Assistance in ALL Stages of your PhD Research in VLSI from Topic Selection to Thesis Submission.

- Creating 100% confident in submitting your thesis work.

- Our experienced professionals support you in your research works.

- Providing complete solutions for the Research Scholars in many advanced domains.

Technologies used in VLSI:

- Modelsim 6.5b Simulator

- Xilinx ISE 10.1 System generator

III. Quartus 11.1

- Tanner v7 EDA tool

iii. W-Edit

- Microwind & DSCH v2

VII. P-spice

VIII. LT-spice

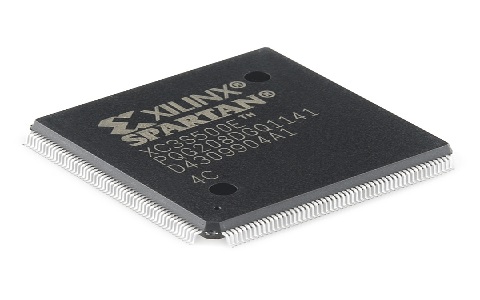

. Spartan IIIe

- Hardware Description Language

. Verilog HDL

CORE AREA OF GUIDANCE:

- Digital signal processing Vlsi

- Image processing Vlsi

III. Wireless Vlsi

- Communication Vlsi

- Testing Vlsi

- Digital cmos Vlsi

VII. low power Vlsi

VIII. Core Vlsi

- Memory Designs

PROJECT SUPPORT:

- Confirmation Letter

- Attendance Certificate

III. Completion Certificate

Preprocessing Work:

- Paper Selection

Identifying the problem:

- Screenshots

III. Simulation Report

- Synthesize Report

Report Materials:

- Block Diagrams

- Review Details

III. Relevant Materials

- Presentation

- Supporting Documents

- Software E-Books

VII. Software Development Standards & Procedure – E-Book

Learning Exposure:

VIII. Programming classes

- Practical training

- Project Design & Implementation

Publishing Support:

XII. Conference Support

XIII. Journal Support

XIV. Guide Arrangements

Vlsi based projects like image processing projects, low power projects, matlab with vlsi projects , cryptography projects, OFDM projects, SDR projects, communication projects, zigbee projects, digital signal processing projects, and also protocol interfacing projects like uart ,i2c,spi projects.

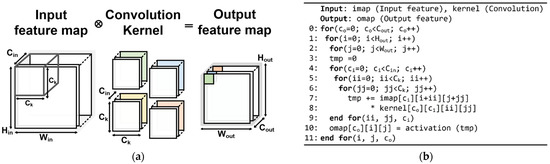

Signal and Image processing projects can be simulated by using Modelsim 6.5b and synthesized by Xilinx 10.1 using Spartan IIIe fpga and by Quartus 11.1using altera de2 fpga. In image processing projects, the input image or video can be converted to coefficients using Matlab. Low power projects can be designed using Tanner, Microwind and spice tools.

We spotlights on imparting an overall exposure to the concept and design methodologies of all major aspects of vlsi engineering relevant to industry needs and ground-breaking thoughts with 100% pure accuracy.

latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design low power testing bist latest research topics in vlsi design latest latest research topics in vlsi design area latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design

Information

- Author Services

Initiatives

You are accessing a machine-readable page. In order to be human-readable, please install an RSS reader.

All articles published by MDPI are made immediately available worldwide under an open access license. No special permission is required to reuse all or part of the article published by MDPI, including figures and tables. For articles published under an open access Creative Common CC BY license, any part of the article may be reused without permission provided that the original article is clearly cited. For more information, please refer to https://www.mdpi.com/openaccess .

Feature papers represent the most advanced research with significant potential for high impact in the field. A Feature Paper should be a substantial original Article that involves several techniques or approaches, provides an outlook for future research directions and describes possible research applications.

Feature papers are submitted upon individual invitation or recommendation by the scientific editors and must receive positive feedback from the reviewers.

Editor’s Choice articles are based on recommendations by the scientific editors of MDPI journals from around the world. Editors select a small number of articles recently published in the journal that they believe will be particularly interesting to readers, or important in the respective research area. The aim is to provide a snapshot of some of the most exciting work published in the various research areas of the journal.

Original Submission Date Received: .

- Active Journals

- Find a Journal

- Proceedings Series

- For Authors

- For Reviewers

- For Editors

- For Librarians

- For Publishers

- For Societies

- For Conference Organizers

- Open Access Policy

- Institutional Open Access Program

- Special Issues Guidelines

- Editorial Process

- Research and Publication Ethics

- Article Processing Charges

- Testimonials

- Preprints.org

- SciProfiles

- Encyclopedia

Journal Menu

- Electronics Home

- Aims & Scope

- Editorial Board

- Reviewer Board

- Topical Advisory Panel

- Instructions for Authors

- Special Issues

- Sections & Collections

- Article Processing Charge

- Indexing & Archiving

- Editor’s Choice Articles

- Most Cited & Viewed

- Journal Statistics

- Journal History

- Journal Awards

- Society Collaborations

- Conferences

- Editorial Office

Journal Browser

- arrow_forward_ios Forthcoming issue arrow_forward_ios Current issue

- Vol. 13 (2024)

- Vol. 12 (2023)

- Vol. 11 (2022)

- Vol. 10 (2021)

- Vol. 9 (2020)

- Vol. 8 (2019)

- Vol. 7 (2018)

- Vol. 6 (2017)

- Vol. 5 (2016)

- Vol. 4 (2015)

- Vol. 3 (2014)

- Vol. 2 (2013)

- Vol. 1 (2012)

Find support for a specific problem in the support section of our website.

Please let us know what you think of our products and services.

Visit our dedicated information section to learn more about MDPI.

VLSI Architectures for Wireless Communications and Digital Signal Processing

- Print Special Issue Flyer

Special Issue Editors

Special issue information, benefits of publishing in a special issue.

- Published Papers

A special issue of Electronics (ISSN 2079-9292). This special issue belongs to the section " Circuit and Signal Processing ".

Deadline for manuscript submissions: closed (31 August 2022) | Viewed by 17630

Share This Special Issue

Dear Colleagues,

Due to the relentless growth of computational complexity, state-of-the-art technologies cannot be realized unless they are accelerated by very-large-scale-integration (VLSI) circuits. For instance, 5G telecommunications necessitate application-specific integrated circuits (ASICs) to achieve data rates over tens of gigabits per second. The Internet-of-Things (IoT) systems connecting a massive number of edge devices also demand highly efficient hardware to accommodate data transfer within a few milliseconds under a limited power budget. Computer-vision applications based on deep neural networks are so computationally intensive that they incur orders-of-magnitude more operations than ever before. To facilitate the realization of such cutting-edge technologies, considerable attention should be paid to the development of efficient VLSI architectures.

This Special Issue solicits original and unpublished papers on high-performance and low-power VLSI architectures and the relevant algorithmic optimizations in the field of wireless communications and digital signal processing.

The topics of interest include but are not limited to:

- VLSI architectures for 5G and 6G telecommunications;

- FPGA and ASIC implementations of signal-processing systems;

- Baseband signal processing for communication systems;

- Circuits and systems for the Internet-of-Things (IoT);

- VLSI architectures for machine learning and artificial intelligence;

- Application-specific instruction-set processors for digital signal processing;

- Hardware-friendly algorithms and optimization techniques;

- Embedded systems on chip (SoCs) for signal-processing applications.

Prof. Dr. Byeong Yong Kong Prof. Dr. Hoyoung Yoo Guest Editors

Manuscripts should be submitted online at www.mdpi.com by registering and logging in to this website . Once you are registered, click here to go to the submission form . Manuscripts can be submitted until the deadline. All submissions that pass pre-check are peer-reviewed. Accepted papers will be published continuously in the journal (as soon as accepted) and will be listed together on the special issue website. Research articles, review articles as well as short communications are invited. For planned papers, a title and short abstract (about 100 words) can be sent to the Editorial Office for announcement on this website.

Submitted manuscripts should not have been published previously, nor be under consideration for publication elsewhere (except conference proceedings papers). All manuscripts are thoroughly refereed through a single-blind peer-review process. A guide for authors and other relevant information for submission of manuscripts is available on the Instructions for Authors page. Electronics is an international peer-reviewed open access semimonthly journal published by MDPI.

Please visit the Instructions for Authors page before submitting a manuscript. The Article Processing Charge (APC) for publication in this open access journal is 2400 CHF (Swiss Francs). Submitted papers should be well formatted and use good English. Authors may use MDPI's English editing service prior to publication or during author revisions.

- Ease of navigation: Grouping papers by topic helps scholars navigate broad scope journals more efficiently.

- Greater discoverability: Special Issues support the reach and impact of scientific research. Articles in Special Issues are more discoverable and cited more frequently.

- Expansion of research network: Special Issues facilitate connections among authors, fostering scientific collaborations.

- External promotion: Articles in Special Issues are often promoted through the journal's social media, increasing their visibility.

- e-Book format: Special Issues with more than 10 articles can be published as dedicated e-books, ensuring wide and rapid dissemination.

Further information on MDPI's Special Issue polices can be found here .

Published Papers (4 papers)

Further Information

Mdpi initiatives, follow mdpi.

Subscribe to receive issue release notifications and newsletters from MDPI journals

Making Electronics Easy

Top 50 vlsi projects ideas: a guide for final year electronics engineering students.

As you approach your final year in electronics engineering, you're likely on the lookout for a project that not only showcases your skills but also dives deep into the world of cutting-edge technologies. Very Large Scale Integration (VLSI) projects offer a perfect opportunity for exploration, allowing you to work on intricate integrated circuits that bring theory to life.

Below, we've curated a list of 50 VLSI projects designed to inspire and challenge you in your final year.

Starting with the Basics:

1. low power sram design.

Picture this: a Static Random Access Memory (SRAM) module that's not only efficient but also power-conscious. Dive into the world of low-power design and performance optimization.

2. Design of a 4-bit Arithmetic Logic Unit (ALU)

Imagine creating a 4-bit Arithmetic Logic Unit capable of handling arithmetic and logical operations with finesse. It's like giving your circuit a mini-brain!

3. VLSI Implementation of FFT Algorithm

Ever wondered how your favorite audio player processes signals so fast? Explore the Fast Fourier Transform (FFT) algorithm in VLSI for efficient signal processing.

4. Design and Implementation of Carry Select Adder

Get ready to design a Carry Select Adder that not only does the math but does it with speed and minimal power consumption.

5. Design of Low Power Multiplier

Think about a multiplier that's not just fast but also mindful of power usage. Dive into the challenge of designing a low-power multiplier.

6. VLSI Design of CORDIC Algorithm

Let's journey into the world of trigonometric functions with the implementation of the Coordinate Rotation Digital Computer (CORDIC) algorithm in VLSI.

7. Design of a Low-Power Comparator

Meet the low-power comparator, your go-to choice for energy-efficient comparisons in various applications.

8. Implementation of a Finite State Machine (FSM)

What if your circuit could understand and respond based on different states? Welcome to the world of Finite State Machines (FSMs)!

9. Design of a Low Power 8-bit Shift Register

Imagine an 8-bit shift register that not only does its job but does it while sipping on power. Dive into the intricacies of low-power design.

10. VLSI Design of a Digital Filter

Ever wondered how digital filters work? Explore their implementation in VLSI for applications in signal processing.

These projects aren't just about circuits and algorithms; they're about giving life to your ideas and making an impact in the world of technology.

Beyond the Basics: Innovative Applications of VLSI

Now, let's leap to more innovative applications of VLSI. These projects bridge the gap between theory and real-world scenarios:

11. Low Power VLSI Implementation of I2C Protocol

Ever thought about making your circuits communicate efficiently with minimal power usage? Dive into the implementation of the I2C communication protocol with a focus on energy efficiency.

12. Design of a Low Power D Flip-Flop

Let's create a D flip-flop that's not just a memory unit but a memory unit that's mindful of power consumption. It's all about marrying functionality with efficiency.

13. VLSI Implementation of Manchester Encoder/Decoder

Imagine encoding and decoding data with the efficiency of Manchester techniques. Explore their implementation in VLSI for robust data transmission.

14. Design of VLSI Based RFID System

Ever thought about creating a system that identifies and tracks items using Radio-Frequency Identification (RFID)? Let's bring that idea to life in the VLSI world.

15. Low Power Implementation of DCT (Discrete Cosine

Get ready to design a circuit that performs the Discrete Cosine Transform with speed and minimal power consumption, perfect for image and signal processing.

16. VLSI Design of UART (Universal Asynchronous Receiver-Transmitter)

What if your circuit could communicate serially with other devices? Let's implement the UART communication protocol in VLSI for seamless device interaction.

17. Implementation of Viterbi Decoder

Ever thought about creating a circuit that corrects errors in digital communication? Dive into the world of the Viterbi algorithm for error correction.

18. Design of a Low Power Comparator

Meet the low-power comparator again, but this time with a focus on low-energy comparisons in various applications.

19. VLSI Design of Parallel Prefix Adder

Think about designing an adder that's not just fast but also efficient in digital circuits. Welcome to the world of parallel prefix adders.

20. Implementation of AES Algorithm in VLSI

What if you could implement the Advanced Encryption Standard (AES) algorithm for secure data encryption? Let's make it happen!

These projects aren't just about the technicalities; they're about solving real-world problems with the power of VLSI.

Pushing Boundaries with Advanced VLSI Projects

For those seeking more advanced challenges, these projects delve into intricate VLSI applications:

21. Design of a Low Power Memory Controller

Imagine creating a memory controller that efficiently manages data storage and retrieval while being mindful of power consumption.

22. VLSI Design of IIR Filter

Dive into the world of Infinite Impulse Response (IIR) filters, offering a versatile solution for signal processing applications.

23. Implementation of RISC Processor

Ever thought about designing a processor that simplifies instructions for streamlined computation? Welcome to the world of Reduced Instruction Set Computing (RISC).

24. Design of a Low Power Voltage-Controlled Oscillator (VCO)

Create a low-power Voltage-Controlled Oscillator (VCO) for applications in frequency modulation and synthesis.

25. VLSI Implementation of Cordic-Based Sine and Cosine Generator

Explore the implementation of Coordinate Rotation Digital Computer (CORDIC) algorithms for generating sine and cosine functions.

26. Design of Low Power Clock Gating Circuit

Imagine designing a clock gating circuit that minimizes power consumption during idle periods. It's all about efficient energy usage.

27. VLSI Design of Manchester Carry Chain Adder

Let's create an adder that not only adds but does it efficiently with the Manchester Carry Chain technique.

28. Implementation of Huffman Encoder/Decoder

Ever thought about compressing and decompressing data efficiently? Dive into the world of Huffman coding for data compression.

29. Design of a Low Power Register File

Create a low-power register file for efficient storage and retrieval of intermediate data in processors.

30. VLSI Implementation of Reed-Solomon Encoder/Decoder

Ever wondered about creating a system that corrects errors in digital communication? Explore the implementation of Reed-Solomon codes for error correction.

These advanced projects aren't just about complexity; they're about mastering the art of VLSI design.

Harnessing VLSI for Real-World Applications

As VLSI technology advances, its applications extend to various domains. Consider projects that bridge the gap between VLSI design and real-world applications:

31. Design of a Low Power Pulse Width Modulation (PWM) Controller

Ever thought about efficiently controlling motors and power electronics? Dive into the world of Pulse Width Modulation (PWM) controllers with a focus on low power.

32. VLSI Design of I2S Audio Interface

Imagine creating an audio interface that delivers high-quality sound in digital systems. Let's implement the Inter-IC Sound (I2S) interface for seamless audio communication.

33. Implementation of SHA-256 Algorithm in VLSI

How about implementing a secure hashing algorithm for data security? Dive into the implementation of the Secure Hash Algorithm (SHA-256).

34. Design of a Low Power Successive Approximation ADC

Imagine creating an Analog-to-Digital Converter (ADC) that not only converts signals but does it efficiently with low power consumption.

35. VLSI Implementation of Cordic-Based Sine and Cosine Generator

Explore the world of sine and cosine functions with the implementation of Coordinate Rotation Digital Computer (CORDIC) algorithms.

36. Design of Low Power Phase-Locked Loop (PLL)

Ever wondered about designing a Phase-Locked Loop that's not just precise but also energy-efficient? Let's create a low-power PLL.

37. VLSI Design of Image Edge Detection Processor

Create a processor that detects edges in images for applications in computer vision and image processing.

38. Implementation of Canny Edge Detector

Dive into the world of image processing with the implementation of the Canny edge detection algorithm for robust image analysis.

39. Design of Low Power Current Steering DAC

Ever thought about creating a Digital-to-Analog Converter (DAC) that not only converts signals but does it efficiently with low power consumption?

40. VLSI Implementation of Serial Peripheral Interface (SPI) Controller

Imagine creating a controller that facilitates seamless communication between devices. Dive into the world of the Serial Peripheral Interface (SPI) protocol.

These projects aren't just about circuits; they're about solving real-world problems with the power of VLSI.

Building Foundations for Future Innovation

Now, let's focus on foundational aspects of VLSI design, laying the groundwork for future innovation:

41. Design of a Low Power Multiplexer

Ever thought about creating a multiplexer that not only routes data but does it efficiently with low power consumption? Dive into the world of low-power design.

42. VLSI Design of GMSK Modulator/Demodulator

Explore the world of digital communication with the implementation of Gaussian Minimum Shift Keying (GMSK) modulation and demodulation.

43. Implementation of Digital Down-Converter (DDC)

Ever wondered about creating a Digital Down-Converter for applications in digital signal processing? Dive into the world of frequency conversion.

44. Design of Low Power Voltage-Controlled Current Source

Create a current source that not only provides a steady current but does it efficiently with low power consumption.

45. VLSI Implementation of Direct Digital Synthesizer (DDS)

Ever thought about creating a synthesizer that precisely generates frequencies in digital systems? Dive into the world of Direct Digital Synthesis.

46. Design of Low Power Content Addressable Memory (CAM)

Imagine creating a Content Addressable Memory (CAM) that not only stores data but does it efficiently with low power consumption.

47. VLSI Design of FFT Processor for Audio Processing

Ever wondered about efficiently processing audio signals in digital systems? Dive into the world of a dedicated FFT processor for audio processing.

48. Implementation of LDPC Decoder

Explore the world of error correction in digital communication with the implementation of a Low-Density Parity-Check (LDPC) decoder.

49. Design of a Low Power Voltage Reference Circuit

Ever thought about creating a voltage reference circuit that not only provides a stable voltage but does it efficiently with low power consumption?

50. VLSI Implementation of High-Speed Divider

Imagine creating a divider that not only divides but does it efficiently with high speed. Dive into the world of high-speed division.

These foundational projects aren't just about circuits; they're about laying the groundwork for future innovation in VLSI.

In Conclusion

As you embark on your VLSI project journey in your final year of electronics engineering, remember that these projects are not just about circuits and algorithms; they're about bringing your ideas to life. They're about solving real-world problems and contributing to the ever-evolving landscape of technology.

So, embrace the challenges, customize the projects based on your interests, and let your creativity shine. Your final year is not just a culmination of your academic journey; it's a platform for you to make a lasting impact in the world of VLSI technology.

Here's to a rewarding and innovative final year in electronics engineering!

- Project Ideas

Related Posts

Top 50 Wireless Sensor Network Projects for Engineering Students

Top 50 PIC Microcontroller Projects for Engineering Students

Top 50 PLC Projects for Engineering Students

Advertisement

Special issue: 26th international symposium on VLSI design and test 2022

- Published: 08 September 2023

- Volume 116 , pages 1–3, ( 2023 )

Cite this article

- Ambika Prasad Shah 1 &

- Sudeb Dasgupta 2

603 Accesses

3 Altmetric

Explore all metrics

Avoid common mistakes on your manuscript.

1 Introduction

The increasing versatility, performance, compactness and power efficiency of today’s electronic systems is achieved by pushing technology to its physical limits; systems are increasing in size and complexity, comprising thousands of subsystems made of billions of devices. The devices themselves have become smaller and smaller and have reached the atomic scale.

This Special Issue aimed at continuing the discussion about the research activities and related findings carried out the 26th International Symposium on VLSI Design and Test (VDAT-2022) held in Jammu, India, July 17- 19th 2022 with the theme of “Chips to Startup for sustainable development”. Therefore, this Special Issue focuses on the following areas:

Emerging Devices and Material Technologies.

VLSI Circuit and System Design.

IC Reliability, Security and Quality.

CAD for VLSI, Testing and Verification.

FPGA based Design and Embedded Systems.

2 Topics of the special issue

This special issue comprises 7 articles selected after a rigorous review process of the extended versions of papers presented at VDAT-2022. Accepted articles covers various aspects of microelectronics devices, ADC, in-memory computation, reliability and security in integrated circuits, various architectures and devices, and focusing at different levels of abstraction from device level to system level.

Paper “Design of a tunable delay line with on-chip calibration to generate process-invariant PWM signal for in-memory computing” by Kavita Monga et al. [ 1 ] address the two major issues with the in-memory computation. For precise operation, the applied input signals must be stable and during the input signal generation is the deviation in the width values due to process, voltage, and temperature variations. Authors have proposed to design a tunable delay line that provides a linear PWM signal corresponding to an input vector which is further utilized to perform local computation in memory.

Paper “Cadmium sulfide deposition suited for photo pattern-based SAW device” by Rahul Sharma et al. [ 2 ] demonstrates a surface acoustic wave (SAW) device based on photopatterned interdigital transducer (IDT) created on a cadmium sulfide layer deposited over a lithium niobate substrate using two methods, viz. chemical bath deposition (CBD) and spin-coating. I–V characteristics are measured for photo pattern-based SAW devices with different electrode separation widths.

Paper “Design of a high precision CMOS programmable gain and data rate delta sigma ADC” by Mohd Asim Saeed et al. [ 3 ] presents a general purpose high precision Delta Sigma (ΔΣ) ADC with a common mode rejection of 100 dB, developed for data acquisition of sensors used in a satellite launch vehicle telemetry system. The ADC is also equipped with on chip offset and gain calibration features to reduce the offset and gain errors.

Paper “Performance analysis of nanosheet transistor with drain/source extension and high-k spacer optimizations for analog applications” by Arvind Bisht et al. [ 4 ] proposes an optimized Nanosheet Transistor (NSHT) with an inner high-k spacer and an underlap region. A symmetric dual-k spacer structure and an undoped underlap region are incorporated into the baseline device to optimize it for better performance. The analog performance of the optimized NSHT is compared with the performance of the baseline NSHT device across the design space.

Paper “A novel routing algorithm for GNR based interconnect considering area optimization, interconnect-reliability and timing issues” by Subrata Das et al. [ 5 ] propose an algorithm for the routing of Graphene nanoribbon based interconnect considering minimization of grid area and improvement of interconnect-reliability as the optimization goals with minimum increase in interconnect resistance and delay.

Paper “BTI resilient TG-based high-performance ring oscillator for PUF design” by Shubhang Srivastava et al. [ 6 ] propose a new energy-efficient and aging resilient inverter and ring oscillator based on an aging resilient inverter design. The proposed inverter is 22.57% less power-consuming and 16% faster than the conventional Aging Resilient inverter while showing nearly identical aging characteristics without significant increment in area overhead. Authors also designed ring oscillator from the proposed inverter shows nearly 1.5% higher frequency than the conventional aging resilient ring oscillator for the same number of inverter stages.

Paper “Efficient hardware implementations of Lopez–Dahab projective co-ordinate based scalar multiplication of ECC” by M. Mohamed Asan Basiri [ 7 ] proposes efficient hardware implementations scalar multiplication of Lopez–Dahab projective co-ordinate based ECC in the platforms of application specific integrated circuit (ASIC) and field programmable gate array logic (FPGA). Due to this dual core implementation in FPGA, the throughput of the proposed scalar multiplication in FPGA is greater than various existing designs.

3 Conclusion

All of the papers selected for this Special Issue represent world-leading current research into robust and novel devices, reliability-aware design and hardware security approaches for computing systems and provide interesting and valuable insights into current and future trends and issues within these areas. We hope you will enjoy reading the papers and find them a source of inspiration for your own work.

Monga, K., Shenoy, M. V., Chaturvedi, N., et al. (2023). Design of a tunable delay line with on-chip calibration to generate process-invariant PWM signal for in-memory computing. Analog Integr Circ Sig Process . https://doi.org/10.1007/s10470-023-02169-5 .

Article Google Scholar

Sharma, R., & Nemade, H. B. (2023). Cadmium sulfide deposition suited for photo pattern-based SAW device. Analog Integr Circ Sig Process . https://doi.org/10.1007/s10470-023-02172-w .

Saeed, M. A., Srivastava, R. K., Sehgal, D., et al. (2023). Design of a high precision CMOS programmable gain and data rate delta sigma ADC. Analog Integr Circ Sig Process . https://doi.org/10.1007/s10470-023-02165-9 .

Bisht, A., Pundir, Y. P., & Pal, P. K. (2023). Performance analysis of nanosheet transistor with drain/source extension and high-k spacer optimizations for analog applications. Analog Integr Circ Sig Process . https://doi.org/10.1007/s10470-023-02171-x .

Das, S., Das, D. K., & Pandit, S. (2023). A novel routing algorithm for GNR based interconnect considering area optimization, interconnect-reliability and timing issues. Analog Integr Circ Sig Process . https://doi.org/10.1007/s10470-023-02170-y .

Srivastava, S., Verma, A., & Shah, A. P. (2023). BTI resilient TG-based high-performance ring oscillator for PUF design. Analog Integr Circ Sig Process . https://doi.org/10.1007/s10470-023-02180-w .

M. Mohamed Asan, Basiri Efficient hardware implementations of Lopez–Dahab projective co-ordinate based scalar multiplication of ECC. Analog Integrated Circuits and Signal Processing . https://doi.org/10.1007/s10470-023-02179-3

Download references

Acknowledgements

We sincerely thank all the reviewers for helping us in reviewing the papers in time. We also thank all the staff members of Analog Integrated Circuits and Signal Processing journal for their effortless support. Last but not the least we thank the Editor-in-Chief and handling editor for their help and support throughout the entire process.

Author information

Authors and affiliations.

IC-ResQ Lab, Electrical Engineering Department, Indian Institute of Technology Jammu, Jammu, 181221, J&K, India

Ambika Prasad Shah

Electronics and Communication Engineering Department, Indian Institute of Technology Roorkee, Uttarakhand, 247667, India

Sudeb Dasgupta

You can also search for this author in PubMed Google Scholar

Corresponding author

Correspondence to Ambika Prasad Shah .

Additional information

Publisher’s note.

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Reprints and permissions

About this article

Shah, A.P., Dasgupta, S. Special issue: 26th international symposium on VLSI design and test 2022. Analog Integr Circ Sig Process 116 , 1–3 (2023). https://doi.org/10.1007/s10470-023-02184-6

Download citation

Published : 08 September 2023

Issue Date : August 2023

DOI : https://doi.org/10.1007/s10470-023-02184-6

Share this article

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

- Find a journal

- Publish with us

- Track your research

IEEE Account

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

Top 5 VLSI Projects For Final Year Students that Boost Your Job Hunt

Author: ramya.

Introduction: The Importance of VLSI Projects for Final Year Students

VLSI projects for final year students serve as a critical bridge to their job hunt. As the technology landscape rapidly evolves, employers seek candidates who possess not only theoretical expertise but also hands-on experience. Engaging in VLSI projects showcases a student's ability to design and implement complex integrated circuits, which is a crucial skill in the semiconductor industry. A robust project demonstrates practical problem-solving, innovation, and adaptability—qualities that stand out on a resume and during interviews. In this article, we present the top five VLSI projects for final year ECE students that can significantly bolster their job hunt prospects.

Design and Implementation of a Low-Power Digital FIR Filter using FPGA

Project Description:

The project involves the following key phases:

FIR Filter Design

Select the filter specifications (such as filter order, cutoff frequency, and desired response characteristics).Design the filter coefficients using appropriate windowing techniques (e.g., Hamming, Blackman) to meet the desired frequency response. Implement the filter transfer function in a digital format suitable for FPGA implementation.

FPGA Platform Selection:

Choose an FPGA development board that suits the project requirements in terms of available resources, I/O interfaces, and power efficiency.

Familiarize yourself with the FPGA's architecture and design tools.

FPGA Implementation:

Develop the FIR filter logic using a Hardware Description Language (HDL) like VHDL or Verilog.

Optimize the design for low-power operation by employing techniques such as clock gating, power gating, and fine-grained power management.

Ensure the filter meets the timing constraints and resource limitations of the chosen FPGA.

Verification and Testing:

Simulate the design using simulation tools to verify its functionality and performance.

Use representative input signals to validate that the filter produces the expected output.

Perform hardware testing on the FPGA board, comparing results with simulation outcomes.

Power Analysis and Optimization:

Utilize FPGA power analysis tools to measure the power consumption of the FIR filter implementation. Identify power-hungry areas and apply design modifications to further reduce power consumption. Balance power optimization with filter performance to achieve the desired trade-off.

Documentation and Presentation:

Create comprehensive documentation outlining the project's design, implementation, testing methodology, and results.Prepare a presentation summarizing the project's objectives, methodologies, and outcomes.

Design and Simulation of a High-Speed Serial Data Transceiver with Error Correction Coding

Project Description:

The VLSI mini project for ECE unfolds in the following stages:

Transceiver Architecture Design:

Define the specifications for the serial data transceiver, considering data rate, modulation scheme, and interfacing standards.nSelect an appropriate error correction coding technique (e.g., Reed-Solomon, Turbo codes) suitable for VLSI mini projects in ECE.

Error Correction Coding Implementation:

Implement the chosen ECC technique in a digital format compatible with VLSI design, catering to ECE project requirements.Integrate ECC encoder and decoder modules within the transceiver architecture.

High-Speed Design:

Design the transceiver's high-speed components, including serializers, deserializers, clock recovery circuits, and equalizers. Address signal integrity concerns, considering impedance matching and signal jitter for robust data transmission.

FPGA or ASIC Platform Selection:

Choose between an FPGA or ASIC platform, aligned with VLSI mini projects in ECE, based on factors like development resources and performance requirements.

Simulation and Validation:

Utilize advanced simulation tools suitable for VLSI mini projects in ECE to rigorously verify the transceiver's functionality. Generate test vectors and simulate various scenarios to validate error correction capabilities and high-speed data transmission.

Performance Analysis:

Analyze the transceiver's performance metrics, including bit error rate (BER), throughput, and latency, in accordance with ECE project goals.

Documentation and Presentation:

Undertaking VLSI mini projects for ECE students during their final year can significantly enhance their job prospects in the competitive landscape of today's tech industry. Create detailed documentation elucidating the transceiver's design, ECC integration, simulation methodologies, and performance analysis, catering to VLSI mini projects for ECE .

Develop a presentation summarizing the project's objectives, methodologies, and outcomes for fellow ECE students.

Development of an Energy-Efficient Reconfigurable Digital Signal Processor (DSP)

DSP Architecture Design:

Define the architecture requirements, including data processing capabilities, memory hierarchy, and reconfigurable elements suitable for VLSI based projects in ECE.

Select the target signal processing applications and adapt the DSP architecture accordingly.

Reconfigurable Unit Design:

Design reconfigurable processing units, such as configurable datapaths and functional units, enabling dynamic adaptation to different algorithms.

Develop interfaces and control mechanisms to facilitate reconfiguration based on the application's requirements.

Energy-Efficient Hardware Optimization:

Implement advanced hardware optimization techniques like clock gating, power gating, and dynamic voltage scaling to minimize energy consumption.

Apply pipelining and parallel processing to enhance throughput while maintaining energy efficiency.

DSP Implementation:

Implement the designed DSP architecture using HDL (VHDL or Verilog) suitable for VLSI based projects in ECE. Ensure efficient resource utilization and performance by employing synthesis and place-and-route tools.

Reconfiguration Management:

Develop software or firmware routines for managing reconfiguration based on the signal processing tasks. Design efficient reconfiguration algorithms and control mechanisms to switch between different configurations seamlessly.

Performance Evaluation:

Evaluate the energy efficiency and performance of the reconfigurable DSP using benchmarks relevant to VLSI based projects in ECE. Compare the DSP's performance against traditional fixed-architecture DSPs.

Create comprehensive documentation outlining the DSP architecture, reconfigurable unit design, hardware optimization techniques, and evaluation results.

Prepare a presentation summarizing the project's objectives, methodologies, and outcomes for fellow ECE students.

Design and Verification of a Secure Hardware Cryptographic Module

The project unfolds through the following pivotal stages:

Cryptographic Module Design:

Define the cryptographic operations to be supported, such as encryption, decryption, hashing, and key generation. Select suitable cryptographic algorithms and protocols that align with the best VLSI projects for ECE students . Design the hardware module's architecture, including functional blocks for key management, data processing, and interfacing.

Hardware Implementation:

Develop the cryptographic module's hardware design using HDL (VHDL or Verilog) suitable for VLSI projects in ECE. Integrate the selected cryptographic algorithms within the hardware architecture. Implement security features such as secure key storage and tamper detection mechanisms.

Verification and Validation:

Utilize advanced verification tools and methodologies to rigorously validate the cryptographic module's design. Perform functional simulation, formal verification, and hardware-in-the-loop testing to ensure correct operation and security. Validate compliance with relevant security standards and protocols.

Security Protocol Integration:

Integrate essential security protocols like TLS/SSL or IPsec to ensure secure communication with external systems. Implement protocol-specific logic and interfaces within the cryptographic module.

Performance Evaluation:

Evaluate the cryptographic module's performance in terms of throughput, latency, and resource utilization, aligning with the criteria of the best VLSI projects for ECE students .

Create comprehensive documentation elucidating the cryptographic module's design, verification methodologies, security features, and performance analysis. Prepare a presentation that concisely outlines the project's objectives, methodologies, and achievements for fellow ECE students.

Implementation of a Neural Network-Based Face Recognition System on FPGA

The project unfolds through the following essential stages:

Neural Network Model Selection:

VLSI-based projects for ece hold significant importance, not only for academic achievements but also for career prospectsChoose a suitable neural network architecture for face recognition, such as Convolutional Neural Networks (CNNs) or Deep Convolutional Generative Adversarial Networks (DCGANs).

Determine the model's complexity and requirements to ensure compatibility with FPGA resources.

Dataset Preparation and Preprocessing:

Gather a diverse dataset of facial images for training and validation.

Apply image preprocessing techniques like normalization and augmentation to enhance model performance.

Neural Network Training:

Train the selected neural network using the prepared dataset to learn face features and representations. Optimize the model's hyperparameters for efficient inference on FPGA.

FPGA Implementation:

Translate the trained neural network model into FPGA-compatible hardware description language (HDL), such as VHDL or Verilog. Partition the neural network's layers onto FPGA resources, utilizing its parallel processing capabilities for real-time inference.

Interface Development:

Design interfaces to capture and preprocess input images from the camera or image source.

Develop the necessary components for interfacing between the neural network hardware and the external environment.

Evaluate the face recognition system's accuracy, speed, and resource utilization on the FPGA.

Compare the results against software-based neural network implementations.

.Create comprehensive documentation detailing the project's architecture, neural network implementation, FPGA design, and performance evaluation. Prepare a presentation summarizing the project's objectives, methodologies, and outcomes for fellow VLSI enthusiasts.

Conclusion:

In conclusion, undertaking impactful VLSI projects for final year not only exemplifies a student's technical prowess but also significantly elevates their job prospects. Engaging in VLSI projects empowers individuals to gain hands-on expertise in complex semiconductor design, fostering career growth in the dynamic semiconductor industry. These projects cultivate practical skills, innovative thinking, and a profound understanding of integrated circuit technologies, positioning professionals for impactful contributions and advancement within the field.

- Top VLSI Companies In Hyderabad

- Top VLSI Companies In Bangalore

- Best 10 VLSI Seminar Topics

- How Professionals working in VLSI startups Move To VLSI MNCs.How to Upgrade Themselves

- How Pay after Placement helps Students Financially in getting Placement in VLSI companies

- Explore Analog Layout Engineer -Salary, Scope and Responsibilities

- What is the RTL Design and Verification Course? Exams, Syllabus, Fee Structure, Placements & More

- Step By Step Procedure To Become RTL Design Engineer

- How Working Professionals Can Do Career Shift To VLSI Domain

- How To Choose the Right Specialization in RTL Design for Your Career

- Common Myths and Misconceptions About VLSI Careers

- How to use Social Media Platforms Effectively for VLSI Job Search

- Which specialization of VLSI is Getting More Interview Calls in 2024?

- Best Website for Applying for Internships in Semiconductor Industries in 2024

- Comparing RTL Design And Physical Design: Which is Best To Choose in 2024?

Related Links

Contact Us On

VLSI FIRST HYDERABAD : 6-3-678/1, 4th floor, #401, Bhan's Aarohan Plaza, Punjagutta, Hyderabad - 500082, Telangana, India [email protected], 9618121212, 9618131313

VLSI FIRST BENGALURU : 2nd Floor, Jai Plaza Symphony, Sector 6, HSR Layout, Near Empire Restaurant Bengaluru, Karnataka, India 560102. [email protected], 9618222144, 9611503690

Operating Hours: Mon 9:00am - 6:00pm Tue 9:00am - 6:00pm Wed 9:00am - 6:00pm Thu 9:00am - 6:00pm Fri 9:00am - 6:00pm Sat by appointment Sun closed

Designed,developed & Marketing by KandraDigital

Copyright © 2022 VLSI FIRST-All Rights Reserved.

Privacy policy

Terms of service

CSE 691 Advanced VLSI Design Spring 2015

Instructor: Professor R. Sridhar, 338K Davis Hall , E-mail: [email protected] Office Hours: Wednesday 1pm-2:30pm

Lecture: Wednesday 6:30 PM – 9:00 PM, Davis 338A

A dvanced VLSI Design is a course that focuses on high performance, low power reliable VLSI Systems Design. We present advanced topics in the design of VLSI Systems. Topics covered include VLSI Circuit techniques and design methodologies for low power applications, process variation and its impact on very deep submicron designs, interconnects, clocking and synchronization, timing issues in digital circuits, and memory & array structures. Emphasis will be on very deep submicron CMOS designs, high speed design styles, timing, arithmetic building blocks, impact of interconnects, signal integrity and power consumption, with added focus on SoC (System on Chip) designs. Prerequisites: Introductory VLSI (CSE493/CSE593) Reference Books:

- Digital Integrated Circuits, Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic´. Second Edition, A Prentice-Hall, 2003

- Additional References: Research papers from leading Conferences and journals .

Grading: Letter grades carry the normal numerical values (90+ = A, 80+ = B, 70+ = C, 60+ = D). Curving may be applied if deemed appropriate by the instructor. Plus/Minus grades will be given. 30% Exam; 15% Homework ; 55% Project; Term paper and presentation. Miscellaneous: A project will be assigned and is due at the end of the semester. The project will incorporate high performance VLSI principles. A term paper and a detailed presentation are due towards the later part of the semester. The topic for the project and the term paper will be selected in consultation with the Professor.

WatElectronics.com

VLSI Projects for Engineering Students

October 9, 2021 By WatElectronics

Very Large Scale Integration Technology (VLSI) is an IC technology, designed by integrating a large number of electronic components such as logic gates , transistors , FET’s , etc. This technology mainly focuses on three major design and physical constraints related to an electric circuit like power, area, and speed. Some of the important VLSI Projects are mentioned below. A few of the VLSI platforms that are currently upcoming are FPGA applications, SOCs, and ASIC designs.

The list of VLSI Projects using wireless, sensors, home automation, Xilinx, Mathlab, SOC, Bluetooth & other projects are discussed below. These projects are very helpful for beginners, diploma students, and engineering students.

VLSI Projects using Verilog

Verilog is one of the software languages used in VLSI technology for defining electronic circuits and their system of design. It represents the electronic circuit design by simulating the program line of code, for representing analysis of test result in terms of positive or negative and also syntheses logic.

The list of VLSI projects based on Verilog code includes the following.

1). Design of Low Power and Enhance Speed Multiplier and Accumulator With SPST Adder in Verilog

The performance of an electronic device depends mainly on power and device heating. The aim of this project is to minimize power factors and improve the speed of MAC using the Spurious Power Suppression Technique over a modified version of the Booth type encoder .

2). Design of Hamming Type Code using FPGA in Verilog

The aim of this project is to design hardware for implementing Hamming based code for encoder and decoder systems over wireless communication . It uses FPGA on which code written in VHDL of Xilinx is executed.

3). Gabor Type Filter for Biometric Recognition with Verilog HDL

The aim of this project is to design a smart biometric fingerprinting system using Gabor filter on the VLSI project platform. This project is coded grayscale filter which is a part of Gabor filter design in VHDL language and executed on FPGA .

4). Enhanced Speed and Minimum Complexity Design of a Reed Solomon Type Decoder

The aim of this project is to design a simple Reed Solomon type decoder using VLSI technology. This project uses the Berlekamp Massey type algorithm , which is programmed in Verilog HDL. Reed Solomon decoder provides enhance speed.

5). Design and Implementing Vending Machine in Verilog HDL

The aim of this project is to design a vending machine using VLSI technology . The designed machine is programmed in VHDL and dumped on FPGA that gives speed response than microcontroller type VM.

VLSI Projects using Xilinx Software

Xilinx Integrated Synthesis Environment is a tool designed for analyzing HDL and synthesizing Xilinx. Its purpose is to develop embedded based firmware for the Xilinx class of CPLD and FPGA IC technology products. They aid developers to compile circuit designs and allow the configuration of the target devices.

VLSI Projects Using Xilinx Software

The list of VLSI projects based on Xilinx software includes the following.

1). Design of TIC TAC TOE Game on Spartan3 Type FPGA using Image Processing

The aim of this project is to design a fun game board called Tic Tac Toe for two players using VHDL. It uses a screen board, LED bulbs, wires, FPGA, sensors , and wires. programmed playing board and FPGA need to be interfaced with the playing board using Xilinx.

2). BPSK Type Implementation on Xilinx System Generator using Spartan3 FPGA Image Processing Kit

The aim of this project is to design BPSK keying modulation type and demodulation type using the Matlab platform. Components used in this project are, FPGA, Matlab, multiplexers , filters such as FIR, and comparators . It is designed on Matlab and generated on SPARTAN.

3). Design QPSK And Synthesizing Its Result

The aim of this project is to design and implement QPSK modulation for satellite based radio applications. This project designs QPSK logic using reverse gate logic executed on Xilinx with VHDL code.

4). Implementation of Bus Based Bridge for Connecting AHB and OCP Bus

The aim of this project is to design a communication bus to connect the other two busses on SOC applications. Components used in this project are SOC, AHB bus, OCP ( Open Core Protocol) bus, and software Xilinx.

5). Design of a Live Traffic Light Based Control System using Xilinx

The aim of this project is to design and implement VLSI code on FPGA for traffic light signals. Components used in this project are FPGA, LED bulbs red, yellow, and green; software Xilinx. The code in this project is written in VHDL

6). Design of OFDM System using IFFT and FFT Transfer Functions

The aim of this project is to design an OFDM system employing FFT and Inverse FFT signal processing on the VLSI platform. This project is written in VHDL coding language and simulated on Xilinx.

7). Floating Point Based Fused Addition, Subtraction, and Fused Dot type Product Units Design

The aim of this project is to design and simulate the parallel operation of floating point type add, subtract, and multiplication type operation using floating type point add, multiplication, and subtract dot product based units in parallel on Xilinx.

8). FPGA Based Mutual Authentication Type Protocol with Modular Arithmetic

Security systems are designed in a smart way they provide access only to authenticators. The aim of this project is to design a higher enhanced protocol for security applications like RFID tags and readers using the VLSI platform programmed in VHDL and simulated on Xilinx.

VLSI Projects using VHDL

A Hardware Description Language (VHDL) is a software program for Very High Speed Integrated Circuit (VHSIC). The purpose of this language is to define the functioning of electronic components on designed circuitry. This language was designed by IEEE and containing VHDL 1987 and 1993 versions for the design of hardware and developing test entities in order to verify hardware behavior.

The list of VLSI projects based on VHDL code includes the following.

1). VGA Type Bouncing Ball Interfacing with Spartan3 Type FPGA for Image Processing Kit

The aim of this project is to design a smart system for VGA on VLSI technology. It uses VGA, bouncing ball, Spartan 3 type FPGA, and connecting wires. The designed hardware programmed using VHDL provides an efficient system with multiple screen pixel display up to WXGA 1280 by 800.

2). Generating PWM Type Signal With Variable Type Duty Cycle on FPGA

The aim of this project is to design and implement a voltage controller PWM using FPGA. Components used in this project are FPGA, PWM signal generator , and software platform VHDL. This system generates a higher value of frequency at the dynamic duty cycle.

3). Implementation of Digital Type Clock with Spartan3an Type FPGA Evaluation Kit

The aim of this project is to design a smart digital clock using VLSI technology. Components used in this project are FPGA, crystal, programming platform VHDL, 2 by 16 LCD, and 50 Hz clock generating circuit. The advantage of this clock is it is portable and displays accurate values.

4). Design of AMBA with AHB BUS Compliant Type Memory Controller

The aim of this project is to design a controller system for controlling CPUs memory containing Read Only Memory and Static Random Access Memory on an AMBA BUS using VLSI technology. This project uses VHDL software for synthesizing results.

5). Design of FPGA based 32-bit Floating Type Point Arithmetic Unit

The aim of this project is to design and implement a floating point number using an arithmetic unit on the VLSI platform. The components used in this technology are FPGA, ALU unit, software code written in VHDL, and also simulated using MAT Lab.

6). Design of a Field Programmable Type CRC Circuit Architecture and Synthesize Architectural Result

The aim of this project is to design and implement a Cyclic type Redundancy Check (CRC) computation circuit using VLSI technology. This project obtains multiple serial processing cells using the matrix method. The components used are FPGA, CRC circuit, and VHDL code.

VLSI Projects using MatLab

Matlab is a software tool designed for performing mathematical and logic calculations such as differentiation, Laplace transform, differential equation, inverse functions, etc. The main purpose of Matlab along with VLSI is to provide solutions for electronic circuits using a causal model type approach.

The list of VLSI projects based on Matlab code includes the following.

1). Design of Fuzzy Type Logic for a Mobile Robot Controller with VHDL

The aim of this project is to design and program a robot using VLSI technology. This robot is programmed to move objects using fuzzy logic on MATLAB software and later translated into VHDL before implementing on hardware.

2). VLSI Implementation of DWT for Image Compression using VLSI

The aim of this project is to design a discrete type wavelet transform (DWT) algorithm using the VLSI platform for image processing type applications. In this project, code is written simulated, and implemented in VHDL and MATLAB.

List of Other VLSI Projects

The list of other VLSI projects includes the following.

1). 3D Technology Based Lifting of Discrete Wavelet Transform (DWT)

The aim of this project is to design an assistant system for high quality image generation system using VLSI technology. It uses a 3D based lifting type filter to generate a discrete wavelet using the VLSI programming language; the advantage is no loss of image quality is observed.

2). Design of Enhance Speed for Hardware Efficient 4-Bit SFQ Type Multiplier

The aim of this VLSI project is to design an advanced version of the conventional type booth encoder. This encoder is designed with a 4-bit SFQ (Single Flux Quantum) multiplier, that provides an enhanced speed and performance for critical type delay applications.

3). Design of Universal Based Cryptography Processor Employed in Smart Cards

The aim of this project is to design a smart universal cryptoprocessor for a card system. This project is designed with the public & private keys using a combination of 3 Data Encryption Standard (DES), Advanced Encryption Standard (AES), and Elliptic Curve Cryptography (ECC).

Design of Universal Based Cryptography Processor Employed in Smart Cards

4). Design of An Enhanced Speed and Minimum Power Multiplier with Spurious Type Power Suppression Technique (SPST)

The aim of this project is to design a system to remove spurious signals from the arithmetic unit using a spurious power type suppression method. A multiplier component operating at a greater velocity consumes less power during data communication with the target location.

5). Design of A Lossless Based Data Compression and Decompression Method and Its Hardware Architecture

The aim of this project is to design an architecture for a 2 stage hardware using an Adaptive Huffman algorithm and Parallel dictionary type LZW algorithm (PDLZW). This project mainly focuses on lossless data decompression and compression applications.

6). Design of Minimum Complexity Turbo Type Decoder Architecture Employed in Energy-Efficient Wireless Sensor Networks

The aim of this project is to design a smart power conservation system during wireless communication over a WSN network. This minimizes the power of the LUT type Log BCJJR type algorithm during communication over WSN into a fundamental ADD Compare Select operation.

7). Design of Optimal VLSI Based Architecture to Filter Impulse Type Noise in Image

The aim of this project is to design a noise filtering system for an image processing application. This project is implemented on a VLSI architecture with an edge type preserving filter. This project benefits in terms of image quality.

8). Design of Processor In Type Memory Architecture for Image and Video Compression System

The aim of this project is to design a system with minimum complex processor-in & a memory architecture to aid multimedia applications for compressing the size on applying instructions in a word, one instruction, and other image and video-related data concepts.

9). Design of Symbol Type Rate Timing Synchronization Procedure for Minimum Power Wireless OFDM Systems

The aim of this project is to design a performance enhancing system for a wireless type OFDM system. This method achieves less power consumption via a dynamic type sample timing type controller and a tunable type clock based generator.

10). Bluetooth Technology Based Wireless Type Home Automation System

The aim of this project is to program an FPGA to control home appliances using a mobile phone. Components used in this project are Field Programmable Gate Array (FPGA), lights sensors, and mobile phones. It saves electric power and provides remote users access via mobile.

11). Design of Automation ARM Controller on FPGA

The aim of this project is to design an arm that is controlled using FPGA. It uses Spartab3an, FPGA, mechanical arm, objects, and connectors. FPGA is programmed to move the robot arm and pic the objects. Such kind of robotic arm project is suitable for industrial repetitive tasks.

12). Cloud Technology Based Temperature Monitoring System

The aim of this project is to design a smart temperature monitoring system using VLSI technology. It uses Spartan3an FPGA, Wi-Fi technology, and internet cloud services. Spartan3an broadcast the live temperature status over the internet and stockpiles the data over the cloud.

13). Design of Multiple Channel for UART on FPGA

The aim of this project is to design a multi type channel UART based controller depending on the asynchronous FIFO method with FPGA for scaling and re-configuring the communicating device when required. It uses FPGA Spartan3an and a complex type communication system.

14). Design of Linear Type and Morphological Type Image Filtering with FPGA Image Processing Kit

The aim of the project is to use real-time algorithms such as 2D type morphological and convolution based filters for showcasing image processes for multiple applications. It uses Spartan3 type FPGA, VLSI technology, an image processing module, and connecting wires.

15). Design of PGA Implementation for Distance Measurement using Ultrasonic Sensor on FPGA

Aim of this project is to design smart distance object tracking systems using VLSI technology. It uses an ultrasonic type sensor, Spartan 3FPGA board, a display system, and an alarm. The automation system tracks object and sends to Spartan3 which and displays on the screen.

16). Design of Booth Type Multiplier on Spartan6 FPGA Board

The aim of this project is to design an enhanced version of a multiplier to improve the performance of digital signal processors in terms of speed and area. Components used in this project are Multiplier & Accumulator of Radix 4, Booth type multiplier algorithm, Spartan6 FPGA, and DSP processor.

17). Lifting Type Discrete Wavelet Transform (DWT) on Spartan3 FPGA with Image Processing Kit

The aim of this project is to design lifting type Discrete based Wavelet Transform for discarding Finite Impulsive type Response with finite based continuous filtering steps. This project is implemented on 1 D and 2D technology.

18). Design of Tetrix Type Game on Spartan3 FPGA with Image Processing Kit

The aim of this project is to design an object detection system using FPGA. It uses a space communication system, antenna, Spartan 3, and display system. This system detects if there is any object in the direction of the antenna and shifts the angle in direction of obstacle free.

19). Design of Medical Based Image Fusion on Spartan 3 Type FPGA

The aim of this project is to design a smart image generation system for medical purposes using MAT LAB. This replaces MRI and CT scanning medical device that generates images with noise and disturbances. It uses Spartan3 FPGA, VB software, MAT Lab, and XPS software.

20). Design of Median Type Filter Implementation on Spartan3 Type FPGA with Image Processing Kit

The aim of this project is to design a system to eliminate noise from the image processing system. Components used in this project are median filter, Spartan 3 FPGA, processor kit for image, and a software name 3 by 3 sliding window algorithm .

21). Design of Sobal Edge Detection using Spartan3 Type FPGA

The aim of this project is to design a Sobel edge type detection algorithm for detecting image pixels within a second. Components used in this project are FPGA XC3S200 – 4tq144, Sobel algorithm, Matlab platform, and display system. This system processes 128 by 128 by 8 pixels of grayscale based images.

22). FPGA Implementation of Keyboard Learner using Spartan3 FPGA Image processing Kit

The aim of this project is to design a smart keyboard system using VLSI technology. In this user mainly focus on the screen rather than the keyboard that is when a user types half a word the software displays nearby keywords on the screen and automatically updates the full word based on the movement of the user’s eyes on the screen.

23). Design of PIR Type Security Alert System on Spartan 3an Based FPGA Starter Kit

The aim of this project is to design a smart security system using VLSI technology. The components used in this project are a PIR sensor that detects the motion of a nearby object in a restricted zone, a camera, an FPGA module “Spartan 3”, and a screen. This project allows access entry only to a legitimate user.

24). Design of AES Encryption Algorithm on Spartan6 Type FPGA

The aim of this project is to design highly secure communication over the internet using AES on the VLSI platform. The components used in this project are Spartan 6 FPGA, software platform VHDL, and AES algorithm. The advantage of this project is it provides high security and consumes less power.

25). Design of Wireless Type Temperature Monitoring System using Spartan3an Type FPGA on Starter Kit for Agriculture Application

The aim of this project is to design a temperature monitoring system for agriculture using VLSI technology. The components used in this project are a temperature sensor, FPGA kit, programming platform VHDL, and agriculture land.

26). Design of Enhance Throughput Based VLSI Architecture for Blackman Windowing in Real Time Spectral Analysis

The aim of this project is to design a smart system to generate maximum throughput on the VLSI platform. This project uses Black man windowing instead of using processors such as DSP or ROM. This project is designed using the VHDL programming language.

27). Approximate Based Search CAM for DNA Sequencing and Genome Analysis

The aim of this project is to design and implement a smart system that detects COVID mutant through COVID affected person DNA on VLSI technology. Components used in this project are the VHDL programming platform, DNA sample from a patient, FPGA, and report tracking system.

28). Design of Hardware for Video Type Processing Superblock Based Accelerator

The aim of this project is to design a high speed video processor for real-time based video stream. This system undergoes three stages namely Alpha blending, polynomial transformation, and low pass filtering. The advantage of this project is it provides noise free video quality.

29). Design of Collision Less Robot Processor on VLSI and RFID Technology

The aim of this project is to design an algorithm for aiding robots to walk without colliding with other robots or obstacles in their environment on VLSI technology. Components used in this technology are RFID reader and RFID card, VHDL, processor, and objects.

30). Design of Adiabatic Based Technique for Power-Efficient Logic Circuit Design

A CMOS circuit is built with multiple gates such as NOR and NAND combinations but these circuits have higher power consumption faction. The aim of this project is to replace the CMOS circuit and design advance enhanced logic type circuits using the adiabatic type technique for minimizing and reusing power.

31). Design of Advanced Encryption System (AES) for Improving System Computing Speed

AES provides high encryption of data over digital communication. The aim of this project is to design and implement an AES encryption algorithm on an FPGA board and simulate it in VHDL software. The advantage of this project is it enhances the encryption factor with high-speed communication.

32). Design of AMBA with Advanced High-Performance Bus (AHB) with IP Block

The aim of this project is to design Advanced Microcontroller Bus Architecture (AMBA) with additional bus AHB using VLSI technology. This project is implemented with slave–master modules. Where master is programmed to control their slave’s components.

33). A Multichannel with Multimode RF Type Transceiver using DSM

The aim of this project is to implement RF type multi-channel emitter and collector working in multi-mode via delta type sigma modulator. Components used in this project are VHDL, Delta Sigma type modulator, and RF channel with communicating components.

34). Asynchronous Type Transfer Mode Based Knockout Switch Concentrator

The aim of this project is to design and implement a networking class switch for datagram and virtual type circuit packet network on VLSI technology. Components used are concentrator of asynchronous type transfers knockout switch , the software platform on VHDL and FPGA.

35). Design of Behavioral Synthesis for Asynchronous Type Circuits

The aim of this project is to design and implement asynchronous type circuits and balsa module templates using the VLSI platform. This project synthesis circuit results in behavioral mode.

36). Implementation of Carrying Type Tree Adder

The aim of this project is to design enhance versions of adders such as parallel prefix adders using VLSI technology to minimize power. This project also synthesizes types of carrying tree adders such as sparse kogge-stone, spanning type tree, and kogge type stone adder.

37). Fixed Angle of Rotation using CORDIC Designs

The aim of this project is to design and implement rotating vectors on coordinate rotation type digital based computer method via at stationary and using reference angles. This project is used in applications like image processing, games, and robotics.

38). Design of an SOC Based Permutation Network on a Multiprocessor

The aim of this project is to control traffic on multiprocessor SOC based applications using VLSI technology. This project is mainly designed for real time based applications for providing enhanced device performance of IP communication.

39). Design of VLSI Based Architecture for Visible Type Watermarking on Secure Still Digital Camera (S2DC) Design

The aim of this project is to design and implement a smart chip for a digital camera using VLSI technology. The purpose of this chip in a digital camera is to develop watermarking on images. Components used are the S2DC camera, chip, and VHDL software.

40). Design of Efficient Systolic Type Array Architecture on VLSI

The aim of this project is to design and implement a systolic type array multiplier using the VLSI platform. This designed multiplier can be further used as a binary multiplier to compute binary type multiplications. Components used are FPGA and code written in VHDL.

41). Design of Multi Type Value Logic With Quantum Dot Gate Type FET

The aim of this project is to design and implement a smart 3 stages quantum Dot based Gate FET circuit to handle an increase in a logic bit in logic circuits. This project is used in applications such as decoders and Op-Amps .